MIPI I3C is a scalable, medium-speed, utility and control bus for connecting peripherals to an application processor.

MIPI I3C bus design incorporates key attributes from both I2C-bus and SPI interfaces to provide a unified, high- performance, low-power interface solution that delivers a flexible upgrade path for I2C-bus and SPI system designers I3C takes the best of SPI and I2C Combined

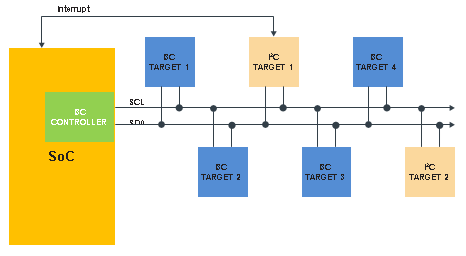

As shown in bus diagram, I2C-bus targets can co-exist with I3C controllers operating at 12.5 MHz, enabling the migration of existing I2C-bus designs to the I3C specification. Conversely, I3C targets operating at typical 400 kHz or 1 MHz I2C-bus speeds can coexist with existing I2C-bus controllers. There can be systems where I3C devices and I2C can exist on the same system bus

Both I2C, I3C are implemented with standard CMOS I/O pins using a two-wire interface, but unlike I2C it supports in-band interrupts enabling target devices to notify controllers of interrupts, a design feature that eliminates the need for a separate general-purpose input/output (GPIO) interrupt for each target, reducing system cost and complexity. Support for dynamic address assignments help minimize pin counts, which is key for accommodating space-constrained form factors. This helps system designers design low pin count system with high performance

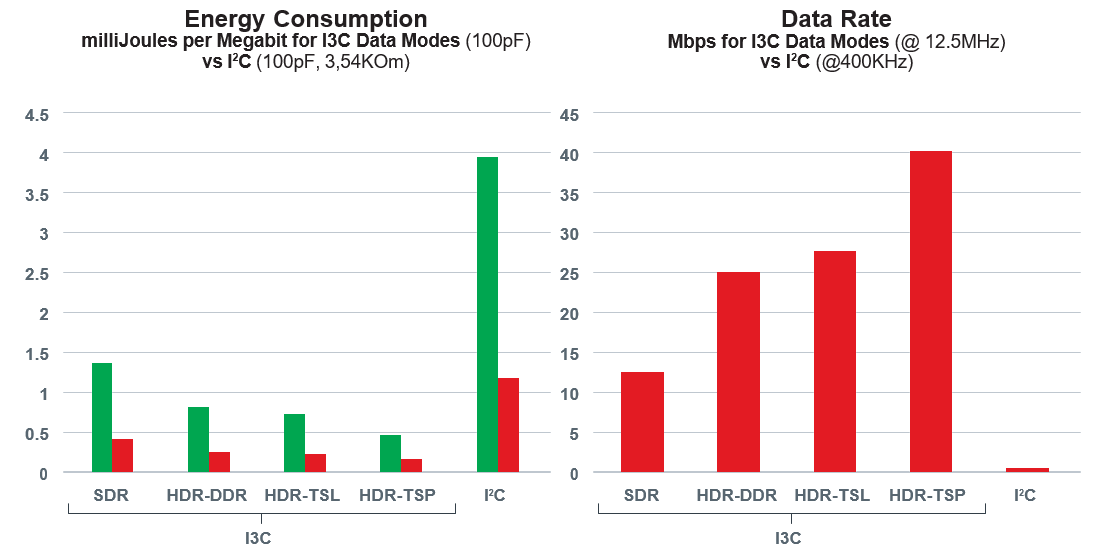

I3C supports a multi-drop bus that, at 12.5MHz, supports standard data rate (SDR) of 10 Mbps with options for high- data-rate (HDR) modes. The net result is that I3C offers a leap in performance and power efficiency compared with I2C as shown in Figure below

Maxvy Technologies provides state of art I3C Controller and many other MIPI IP like I3C master and slave Controller. Maxvy Provides several design and Verification IP for SoC design and development.