MIPI I3C Controller IP Core is fully compliant with the latest I3C specification and delivers high bandwidth and scalability for integration of multiple sensors into mobile, automotive and IoT system-on-chips (SoCs).

The MIPI I3C Controller supports in-band interrupts within the 2-wire interface provides significantly lower pin count, simplifying board design and reducing power and cost of the system.

The MIPI I3C Controller IP is fully backward compatible with I2C, allowing designers to future proof their design, and the I3C controller IP operating modes enable systems with several ICs to efficiently connect to all sensors on a single I3C bus.

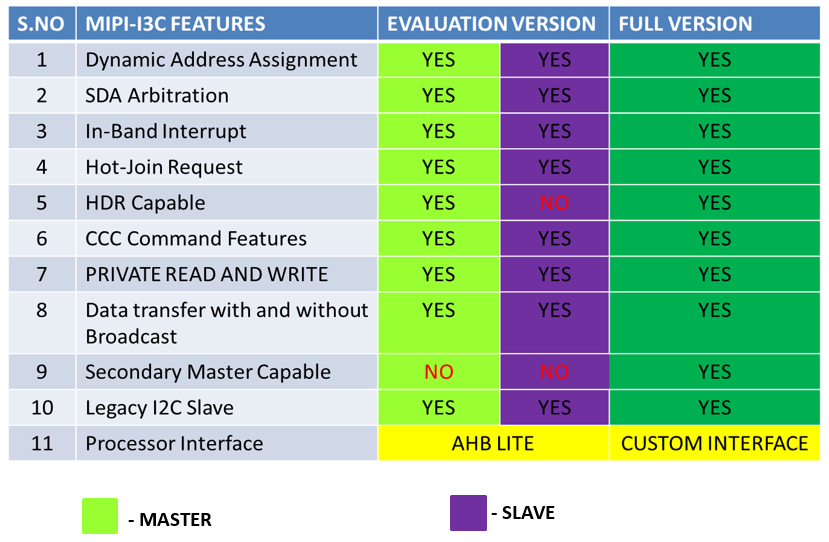

The standard-based ARM® AMBA® Advanced High Performance Bus (AHB) connects the IP to the rest of the SoC offering easy IP integration.

MIPI I3C Controller IP is designed to easily integrate into any SoC offering lowest gate count and quickly fit into any Chip development flow.